Intel is gearing up to unveil its next-generation Diamond Rapids “Xeon” CPUs, which promise significant advancements in CPU architecture. These upcoming processors will feature innovative design elements to enhance performance and efficiency, targeting the needs of modern data centers.

Unveiling New Tiles: CBB and IMH

Emerging details from recent Kernel patches provide a closer look at the architecture of Intel’s Diamond Rapids CPUs. The design introduces two novel tiles: the CBB “Core Building Block” and the IMH “Integrated I/O & Memory Hub.” Unlike its predecessor, Granite Rapids, Diamond Rapids separates the integrated memory controller (IMC) from the compute tile, placing it instead on the IMH tile. Reports suggest that this architecture will support up to two IMH dies.

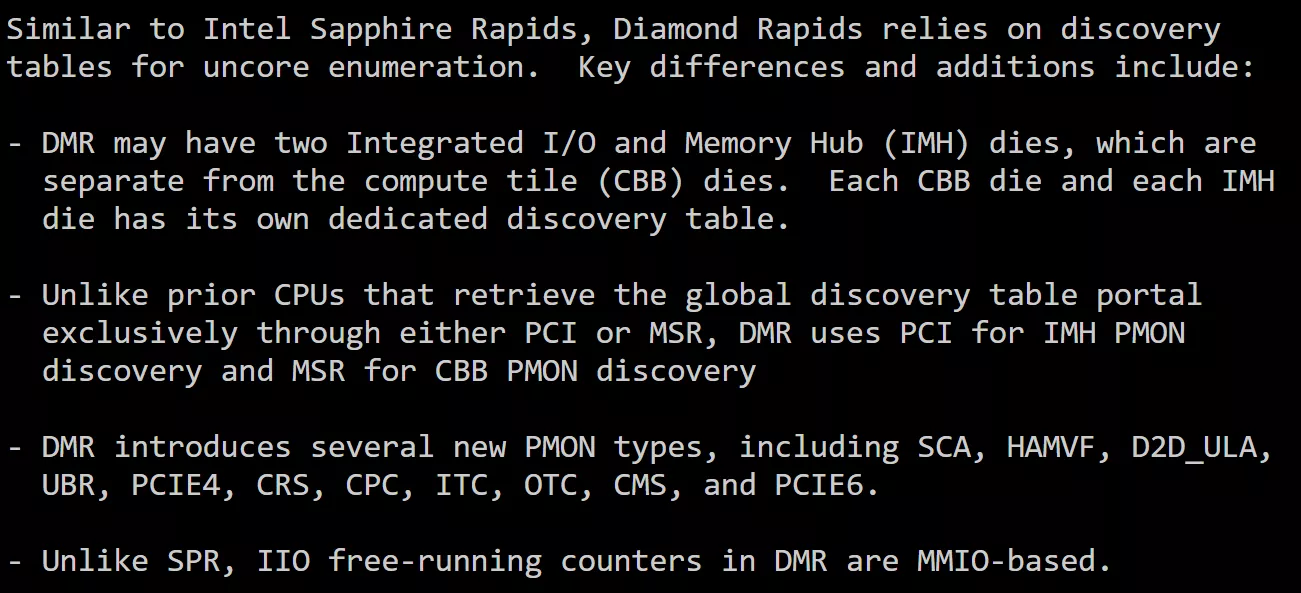

These changes mark a departure from Intel Sapphire Rapids, with Diamond Rapids utilizing discovery tables for uncore enumeration. Key differences include the possibility of dual IMH dies, each with dedicated discovery tables, and the use of PCI for IMH PMON discovery and MSR for CBB PMON discovery. Additionally, Diamond Rapids introduces several new PMON types, including SCA, HAMVF, and PCIE6, among others.

Future Prospects and Specifications

Further insights suggest the inclusion of PCIe Gen6 support, aligning with the latest technology trends set for release in 2026. This support dovetails with next-gen data center CPU platforms like Diamond Rapids and Venice. Earlier information hints at Diamond Rapids “Xeon” CPUs potentially boasting up to 192 cores, with some speculations suggesting as many as 256 cores. While Intel hasn’t confirmed all details, it is expected that these chips will leverage the advanced 18A process node, housing Panther Cove P-Cores.

Platform specifics indicate support for up to 650W TDPs on the LGA 9324 platform, with multi-socket capabilities. Intel aims to launch these groundbreaking Diamond Rapids CPUs by mid- or late-2026.